| Model | Answer, | Page          | <b>1</b> of | Ę |

|-------|---------|---------------|-------------|---|

|       | /       | $\mathcal{O}$ |             |   |

Assiut University Faculty of Engineering EE0513-ELECTRONIC CIRCUITS First Term Final Exam January 2017

Mechatronics Program

**Time: 3 Hours**

Attempt all questions, full mark: 40 Points Question #1: (10 Points)

## Mark True (✓) or False (x)

- **X** 1) Voltage-divider bias is rarely used.

- **X** 2) *h*-parameters are never specified on a datasheet.

- $\checkmark$  3) In a *CE* amplifier, the gain can be stabilized by using a swamping resistor.

- $\checkmark$  4) A differential amplifier amplifies the difference of two input signals.

- **X** 5) A *CB* amplifier has high current gain.

- $\mathbf{X}$  6) When a transistor is saturated, the collector current is minimum.

- $\checkmark$  7) In an amplifier, a coupling capacitor should appear ideally as a short to the signal.

- 8) Class *AB* operation overcomes the problem of crossover distortion.

- 9) Darlington transistors can be used to increase the input resistance of a class AB amplifier.

- $\checkmark$  10) The *JFET* always operates with a reverse-biased gate-to-source *pn* junction.

- **X** 11) The drain current  $I_D$  of a *JFET* becomes zero if  $V_{DS}$  is at the pinch-off voltage.

- **X** 12) Forward transconductance is the change in drain voltage for a given change in gate voltage.

- ✓ 13) A *D*-MOSFET has a physical channel and an *E*-MOSFET has an induced channel.

- $\checkmark$  14) An analog switch is controlled by a digital input.

- **X** 15) If the feedback resistor in an inverting amplifier opens, the gain becomes zero.

- **X** 16) The gain of a voltage-follower is very high.

- **X** 17) An ideal op-amp has very high output impedance.

- $\checkmark$  18) An *R*/2*R* ladder circuit is one form of Digital to Analog Converter.

- $\checkmark$  19) Negative feedback reduces the gain of an op-amp from its open-loop value.

- **X** 20) When a triangular waveform is applied to a differentiator, a sine wave appears on the output.

Model Answer, Page 2 of 5

## **<u>Question #2</u>: (6 Points)** Choose the right answer:

| 1)  | A transistor circuit has $V_{CC} = 12$ V, $V_{BB} = 3$ V, $R_C = 2$ K $\Omega$ , $R_B = 50$ K $\Omega$ , and $\beta_{DC} = 80$ , the transistor is |                                                                                                                   |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| С   |                                                                                                                                                    | <ul><li>(B) being driven into cutoff</li><li>(D) operating nonlinearly</li></ul>                                  |  |

| 2)  | The voltage gain of a common-base amplifier is                                                                                                     |                                                                                                                   |  |

| С   | <ul><li>(A) very low</li><li>(C) the same as a CE</li></ul>                                                                                        | <ul><li>(B) very high</li><li>(D) the same as a CC</li></ul>                                                      |  |

| 3)  | The main advantage of a common-collector amplifier is                                                                                              |                                                                                                                   |  |

| С   | <ul><li>(A) high current gain</li><li>(C) high input impedance</li></ul>                                                                           | <ul><li>(B) high voltage gain</li><li>(D) low input impedance</li></ul>                                           |  |

| 4)  | The main advantage of the class-B amplifier over the class-A one is                                                                                |                                                                                                                   |  |

| D   | <ul><li>(A) higher current gain</li><li>(C) higher power gain</li></ul>                                                                            | <ul><li>(B) higher voltage gain</li><li>(D) higher efficiency</li></ul>                                           |  |

| 5)  | The efficiency of a power amplifier is the ratio of the power delivered to the load to                                                             |                                                                                                                   |  |

| С   |                                                                                                                                                    | <ul><li>(B) the power dissipated in the last stage</li><li>(D) none of these answers</li></ul>                    |  |

| 6)  | The maximum efficiency of a class A power amplifier is                                                                                             |                                                                                                                   |  |

| А   | (A) 25%<br>(C) 75%                                                                                                                                 | <ul><li>(B) 50%</li><li>(D) 78.5%</li></ul>                                                                       |  |

| 7)  | In a JFET, <i>I<sub>DSS</sub></i> is                                                                                                               |                                                                                                                   |  |

| С   | <ul><li>(A) the drain current with the source shorted</li><li>(C) the maximum possible drain current</li></ul>                                     | <ul><li>(B) the drain current at cutoff</li><li>(D) the midpoint drain current</li></ul>                          |  |

| 8)  | $\Box$ The drain current in a JFET is controlled by                                                                                                |                                                                                                                   |  |

| А   |                                                                                                                                                    | <ul><li>(B) the drain-to-source voltage</li><li>(D) the gate current</li></ul>                                    |  |

| 9)  | For a p-channel JFET, drain current in the constant-current region increases when                                                                  |                                                                                                                   |  |

| А   | <ul><li>(A) the gate-to-source bias voltage decreases</li><li>(C) the drain-to-source voltage increases</li></ul>                                  | <ul><li>(B) the gate-to-source bias voltage increases</li><li>(D) the drain-to-source voltage decreases</li></ul> |  |

| 10) | The op-amp common-mode gain is                                                                                                                     |                                                                                                                   |  |

| В   | <ul><li>(A) very high</li><li>(C) always unity</li></ul>                                                                                           | <ul><li>(B) very low</li><li>(D) unpredictable</li></ul>                                                          |  |

| 11) | In a zero-level detector, the output changes state when the input                                                                                  |                                                                                                                   |  |

| С   | <ul><li>(A) is positive</li><li>(C) crosses zero</li></ul>                                                                                         | <ul><li>(B) is negative</li><li>(D) has a zero rate of change</li></ul>                                           |  |

| 12) | In a scaling adder, the input resistors are                                                                                                        |                                                                                                                   |  |

| С   | <ul><li>(A) all the same value</li><li>(C) each proportional to the weight of its input</li></ul>                                                  | <ul><li>(B) all of different values</li><li>(D) related by a factor of two</li></ul>                              |  |

#### Model Answer, Page **3** of **5**

#### **Question #3: (10 Points)**

a) A certain transistor has  $\alpha_{DC} = 0.99$ . If the dc base current is 10 µA, determine  $r_e'$ .

$r_e' = 25 \Omega$

b) An n-channel JFET has  $I_{DSS} = 5$  mA and  $V_{GS(off)} = -8$  V. What value of  $V_{GS}$  is required to set up a drain current of 2.25 mA.

$V_{\rm gs} = -2.63 \ {\rm V}$

c) A certain class A power amplifier has  $V_{CEQ}= 12$  V and  $I_{CQ}= 1$ A. Find the maximum signal power output.

$P_{L(max)} = 6 W$

d) What bias voltage is developed at the base of a transistor if both resistors in a voltage divider are equal and  $V_{CC}=10$ V?

$V_B = 5 V$

e) An n-channel JFET with voltage-divider bias has a gate voltage of 3V, a drain current of 9 mA, and a source resistance of 800  $\Omega$ . Calculate  $V_{GS}$ .

$V_{\rm gs} = -4.2 \ {

m V}$

f) What is the major difference in construction of the D-MOSFET and the E-MOSFET?

# A *D-MOSFET* has a physical channel; while an *E-MOSFET* has an induced channel.

g) A common-emitter amplifier is driving a load resistance  $R_L = 10 \text{ k}\Omega$ . If  $R_C = 2.2 \text{ k}\Omega$ ,  $I_{CQ} = 2.5 \text{ mA}$ ,  $\beta_{ac} = 75$  and  $R_E$  is completely bypassed at the operating frequency. Find the voltage gain.

$A_{\rm v}=-180$

h) If the gate-to-source voltage in an n-channel D-MOSFET is made more negative, what would be the effect on the drain current?

Decreases.

i) What is the major difference in construction of the MOSFET and the JFET?

In *MOSFET*, the gate is isolated from the channel by  $SiO_2$  layer; while in the *JFET*, the gate constructs a reverse biased *pn*-junction with the channel.

j) What is the feedback element in an ideal op-amp integrator?

A capacitance.

Model Answer, Page **4** of **5**

#### **Question #4: (5 Points)**

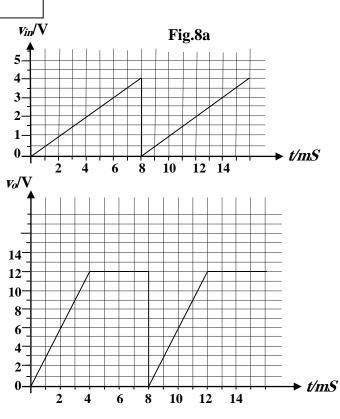

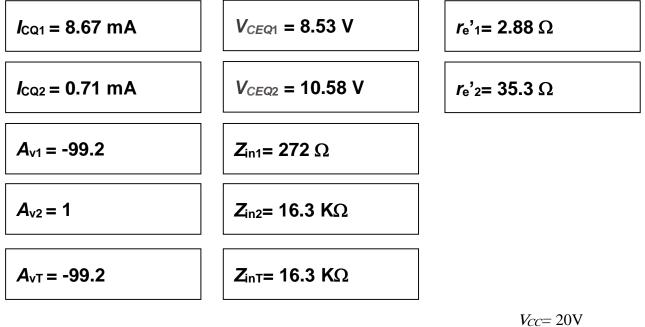

The silicon *npn* transistors used in the two-stage amplifier shown in Fig.4 has  $\beta_{dc} = \beta_{ac} = 100$ .

- a) Find the operating point and  $r'_e$  for each transistor. (2 Points)

- b) Find the voltage gain and input impedance of each stage. (2 Points)

- c) Find the overall voltage gain and input impedance of the amplifier. (1 Point)

39.3 %

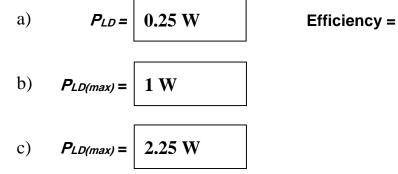

#### **Question #5** (2 Points)

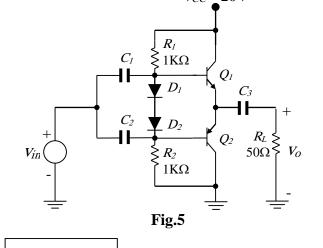

The class AB amplifier in Fig.5 is operating with a single power supply.

- a) Assuming the input peak-to-peak voltage is 10

V; determine the power delivered to the load resistor and the amplifier efficiency. (1 Point)

- b) What is the maximum power that could be delivered to the load resistor? (1/2 Point)

- c) Assume the power supply voltage is raised to 30V. What is the new maximum power that could be delivered to the load resistor? (1/2 Point)

Model Answer, Page **5** of **5**

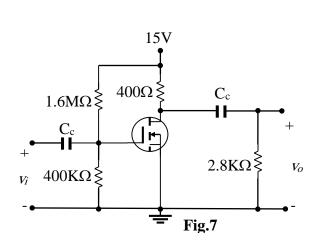

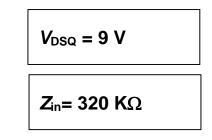

### **Question #6: (3 Points)**

The E-MOSFET used in the common-source amplifier in Fig.6 has  $I_{D(on)} = 135$  mA at  $V_{GS} = 4$  V and  $V_{GS(th)} = 2.5$  V.

- a) Determine the operating point  $V_{GSQ}$ ,  $I_{DQ}$  and  $V_{DSQ}$ .

- b) Calculate the value of the transconductance  $g_m$  at the Q-point.

- c) Determine the voltage gain and input impedance of the amplifier.

$V_{\text{inl}} = 1 \text{V}$

$V_{in2} = 9V.$

$V_{in3} = 2V$

5ΚΩ

$R_2$

۸Ñ

30KΩ

$R_3$

$\sim$

20KΩ

$R_f$

10KΩ

Fig.7

$V_o$

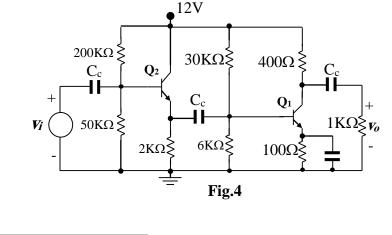

#### **Question #7: (2 Points)**

$g_{\rm m} = 60 \, {\rm mS}$

$V_{GSQ} = 3 V$

- a) Find the output voltage when the indicated input voltages are applied to the scaling adder of Fig.7. (1 Point)

- b) What is the value of the current through  $R_f$ ?

(1 Point)

$I_{DQ} = 15 \text{ mA}$

$A_{v} = -21$

*I<sub>f</sub>* = 0.6 mA

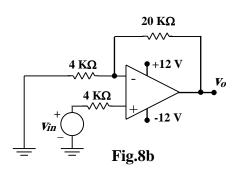

#### **Question #8: (2 Points)**

The voltage waveform of Fig.8a is applied to the non-inverting amplifier of Fig.8b. Sketch the output waveform  $v_o$ .